Flip-flop es un término que pertenece a la electrónica digital y es un componente electrónico que se utiliza para almacenar un solo bit de información.

Representación esquemática de Flip Flop

- Dado que Flip Flop es un circuito secuencial, su entrada se basa en dos parámetros, uno es la entrada actual y el otro es la salida del estado anterior.

- Tiene dos salidas, ambas son complementarias entre sí.

- Puede estar en uno de dos estados estables, 0 o 1.

Diagrama básico de Flip Flop

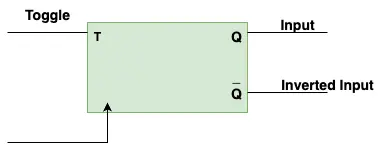

¿Qué es T Flip Flop?

- T flip flop o, para ser precisos, se conoce como Toggle Flip Flop porque puede alternar su salida dependiendo de la entrada.

- t aquí significa Palanca .

- Alternar básicamente indica que el bit se invertirá, es decir, de 1 a 0 o de 0 a 1.

- Aquí, se suministra un pulso de reloj para operar este flop, por lo que es un flip-flop sincronizado.

Construcción de T Flip Flop

Podemos construir T flip de tres maneras, a saber:

- Usando chanclas SR.

- Usando D Flip Flops.

- Usando chanclas JK

Formas de construir T Flip Flop

Veamos la construcción de T Flip Flop usando SR Flip Flops, que requieren 2 puertas AND y 2 puertas NOR como se muestra a continuación:

Diagrama de bloques básico de T Flip Flop

Aquí el diagrama de bloques contiene entradas de alternancia y reloj, Q y Q' son las entradas complementadas.

Funcionamiento de T Flip Flop

Caso 1 : Digamos, T = 0 y el pulso del reloj es alto es decir, 1, entonces la salida de ambos, Y la puerta 1, Y la puerta 2 será 0 , puerta 3 la salida será q y de manera similar puerta 4 la salida será Q' entonces ambos valores de Q y Q’ son los mismos que su valor anterior, lo que significa Estado de retención .

Caso 2 : Digamos, T=1 , entonces la salida de ambas puertas AND 1 será (T * reloj * Q) , y dado que T y el reloj son 1, entonces la salida de la puerta AND 1 será q , y de manera similar la salida de la puerta AND 2 será (T * reloj * Q’) es decir., Q' . Ahora, la salida de la puerta 3 será (Q'+Q)' y digamos que Q' es cero, entonces la salida de la puerta 3 será (0+Q)’ lo que significa Q' y de manera similar la salida de la puerta 4 será (Q+Q’)’ y dado que Q' es cero, la salida de la puerta 4 será Q', lo que significa 0 ya que Q' es cero. Por lo tanto, en este caso podemos decir que la salida alterna, porque T=1 .

Tabla de verdad de T Flip Flop

- Aquí, T es la entrada de alternancia, Q es la entrada del estado presente, Qt+1 es la siguiente salida del estado.

- Desde aquí podemos ver que, siempre que Toggle (T) sea 0, la salida del siguiente estado (Qt+1) es la misma que la entrada del estado actual (Q).

- Siempre que Toggle (T) sea 1, la salida del siguiente estado (Qt+1) será un complemento de la entrada del estado actual (Q), lo que significa que se alterna.

Ecuación característica

- La ecuación característica nos dice cuál será el próximo estado del flip-flop en términos del estado actual.

- Para obtener la ecuación característica, se construye K-Map que se mostrará a continuación:

- Si resolvemos el K-Map anterior, la ecuación característica será Q(n+1) = TQn’ + T’Qn = T XOR Qn

Tabla de excitación

La tabla de excitación básicamente informa sobre la excitación que requiere el flip-flop para pasar del estado actual al siguiente.

- Aquí, siempre que T sea 0, Qt+1 es lo mismo que la entrada Q.

- Y, siempre que T sea 1, Qt+1 es complementario de la entrada Q.

Aplicaciones de T Flip Flop

Existen numerosas aplicaciones de T Flip Flop en el sistema digital, que se enumeran a continuación:

- Contadores : T Chanclas utilizadas en mostradores. Los contadores cuentan la cantidad de eventos que ocurren en un sistema digital.

- Almacenamiento de datos : T Chanclas utilizadas para crear memoria que se utilizan para almacenar datos cuando se apaga la alimentación.

- Circuitos lógicos síncronos : Los flip-flops T se pueden utilizar para implementar circuitos lógicos síncronos, que son circuitos que realizan operaciones con datos binarios basándose en una señal de reloj. Al sincronizar las operaciones del circuito lógico con la señal del reloj mediante flip-flops T, el comportamiento del circuito puede volverse predecible y confiable.

- División de frecuencia : Se utiliza para dividir la frecuencia de una señal de reloj por 2. El flip-flop alternará su salida cada vez que la señal del reloj pase de alta a baja o de baja a alta, dividiendo así la frecuencia del reloj por 2.

- Registros de desplazamiento : Los flip-flops T se pueden utilizar en registros de desplazamiento que se utilizan para desplazar datos binarios en una dirección.

Conclusión

En este artículo comenzamos con los conceptos básicos de las chanclas, lo que en realidad son chanclas y luego discutimos sobre las chanclas T, tres formas en las que podemos construir chanclas T, su diagrama de bloques básico, funcionamiento de las chanclas T. , es la tabla de verdad, la ecuación característica y la tabla de excitación y al final discutimos las aplicaciones de las chanclas T.